# ETL IN MTD DAQ UPDATE

NAOMI GONZALEZ AND HAYDEN SWANSON

# MUX64 FULLY OPERATIONAL ON MTD SW

```

[cmx@serenity-2368-15 mux64]$ python -m src.mtddaqsw.apps.S mux64

Fetching config from: http://localhost:8001/etl_chip_config/Master LPGBT

Success: Received configuration for Master LPGBT

Fetching config from: http://localhost:8001/etl_chip_config/MUX64

Success: Received configuration for MUX64

Calibrated lpgbt ADC. Gain: 1.87109375 / Offset: 502

```

| Channel  | Pin | Voltage   | Comment                                    |

|----------|-----|-----------|--------------------------------------------|

| LV_RB    | 0   | 8.97089   | Low voltage, 9V                            |

| RT2      | 1   | 1.07346   | lpGBT ADC5 (RT2), R2 values is approximate |

| slot0_a4 | 2   | 0.0335031 | VREF3 on module 1                          |

| slot0_a5 | 3   | 0.0335031 | VREF2 on module 1                          |

| slot0_a6 | 4   | 0.0344917 | VREF4 on module 1                          |

| slot0_a7 | 5   | 0.0344917 | VREF1 on module 1                          |

| slot1_a4 | 6   | 0.0335031 | VREF3 on module 2                          |

| slot1_a5 | 7   | 0.0335031 | VREF2 on module 2                          |

| slot1_a6 | 8   | 0.0344917 | VREF4 on module 2                          |

| slot1_a7 | 9   | 0.0335031 | VREF1 on module 2                          |

| slot2_a4 | 10  | 0.0335031 | VREF3 on module 3                          |

| slot2_a5 | 11  | 0.0335031 | VREF2 on module 3                          |

| slot2_a6 | 12  | 0.0335031 | VREF4 on module 3                          |

| slot2_a7 | 13  | 0.0335031 | VREF1 on module 3                          |

No Module connected,

Regular

```

[cmx@serenity-2368-15 mux64]$ python -m src.mtddaqsw.apps.S mux64

Fetching config from: http://localhost:8001/etl_chip_config/Master LPGBT

Success: Received configuration for Master LPGBT

Fetching config from: http://localhost:8001/etl_chip_config/MUX64

Success: Received configuration for MUX64

Calibrated lpgbt ADC. Gain: 1.8671875 / Offset: 502

```

| Channel  | Pin | Reading (raw) | Reading (calib) | Voltage (direct) | Voltage (conv) | Comment                                    |

|----------|-----|---------------|-----------------|------------------|----------------|--------------------------------------------|

| LV_RB    | 0   | 814           | 831.562         | 0.812867         | 8.94153        | Low voltage, 9V                            |

| RT2      | 1   | 533           | 547.952         | 0.535632         | 1.07126        | lpGBT ADC5 (RT2), R2 values is approximate |

| slot0_a4 | 2   | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF3 on module 1                          |

| slot0_a5 | 3   | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF2 on module 1                          |

| slot0_a6 | 4   | 25            | 35.2323         | 0.0344401        | 0.0344401      | VREF4 on module 1                          |

| slot0_a7 | 5   | 25            | 35.2323         | 0.0344401        | 0.0344401      | VREF1 on module 1                          |

| slot1_a4 | 6   | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF3 on module 2                          |

| slot1_a5 | 7   | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF2 on module 2                          |

| slot1_a6 | 8   | 23            | 33.2137         | 0.0324669        | 0.0324669      | VREF4 on module 2                          |

| slot1_a7 | 9   | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF1 on module 2                          |

| slot2_a4 | 10  | 25            | 35.2323         | 0.0344401        | 0.0344401      | VREF3 on module 3                          |

| slot2_a5 | 11  | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF2 on module 3                          |

| slot2_a6 | 12  | 25            | 35.2323         | 0.0344401        | 0.0344401      | VREF4 on module 3                          |

| slot2_a7 | 13  | 24            | 34.223          | 0.0334535        | 0.0334535      | VREF1 on module 3                          |

No Module connected,

Verbose

- DEBUGGED ADC CONVERSION

- CALIBRATED LPGBT ADCs

- VERBOSE OUTPUT OPTION

- PRETTY TABLE PRINT

- PROPER ERROR HANDLING BY USING CUSTOM ERROR EXCEPTIONS

- MUX CHANNELS READ BY CUSTOM NAME OR ONE OF THE 64 PHYSICAL PIN NUMBERS

- VERIFIED ETROC MONITORING - MODULEV0BV

# MUX64 FULLY WORKING ON MTD SW

```

[cmx@serenity-2368-15 mux64]$ python -m src.mtdaqsw.apps.S_mux64

Fetching config from: http://localhost:8001/etl_chip_config/Master LPGBT

Success: Received configuration for Master LPGBT

Fetching config from: http://localhost:8001/etl_chip_config/MUX64

Success: Received configuration for MUX64

Calibrated lpgbt ADC. Gain: 1.86328125 / Offset: 502

```

| Channel  | Pin | Voltage   | Comment                                    |

|----------|-----|-----------|--------------------------------------------|

| LV_RB    | 0   | 8.8689    | Low voltage, 9V                            |

| RT2      | 1   | 1.06906   | lpGBT ADC5 (RT2), R2 values is approximate |

| slot0_a4 | 2   | 0.033404  | VREF3 on module 1                          |

| slot0_a5 | 3   | 0.989387  | VREF2 on module 1                          |

| slot0_a6 | 4   | 0.458723  | VREF4 on module 1                          |

| slot0_a7 | 5   | 0.0343885 | VREF1 on module 1                          |

| slot1_a4 | 6   | 0.033404  | VREF3 on module 2                          |

| slot1_a5 | 7   | 0.033404  | VREF2 on module 2                          |

| slot1_a6 | 8   | 0.033404  | VREF4 on module 2                          |

| slot1_a7 | 9   | 0.033404  | VREF1 on module 2                          |

| slot2_a4 | 10  | 0.0343885 | VREF3 on module 3                          |

| slot2_a5 | 11  | 0.033404  | VREF2 on module 3                          |

| slot2_a6 | 12  | 0.033404  | VREF4 on module 3                          |

| slot2_a7 | 13  | 0.0343885 | VREF1 on module 3                          |

Slot 1

Module,

MTD SW

MODULE OUTPUTS WITH A

A MODULE V0B

CONNECTED!

```

RB configured successfully. Rhett is happy 😊

>>> rb.MUX64.read_channels()

```

| Channel | Pin | Reading (raw) | Reading (calib) | Voltage (direct) | Voltage (conv) | Comment                                    |

|---------|-----|---------------|-----------------|------------------|----------------|--------------------------------------------|

| A0      | 0   | 806           | 564.419         | 0.807337         | 8.86981        | LV RB                                      |

| A1      | 1   | 543           | 559.351         | 0.546776         | 1.09950        | lpGBT ADC5 (RT2), R2 values is approximate |

| mod0_a5 | 3   | 997           | 1018.47         | 0.996565         | 0.995575       | VREF on module 1                           |

| mod0_a6 | 4   | 569           | 583.676         | 0.571544         | 0.571544       | VTEMP on module 1                          |

| mod1_a5 | 7   | 24            | 32.3243         | 0.0306069        | 0.0315976      | VREF on module 2                           |

| mod1_a6 | 8   | 24            | 32.3243         | 0.0315976        | 0.0315976      | VTEMP on module 2                          |

| mod2_a5 | 11  | 25            | 32.3243         | 0.0325883        | 0.0315976      | VREF on module 3                           |

| mod2_a6 | 12  | 25            | 32.3243         | 0.0306069        | 0.0315976      | VTEMP on module 3                          |

Slot 1

Module,

Tamalero

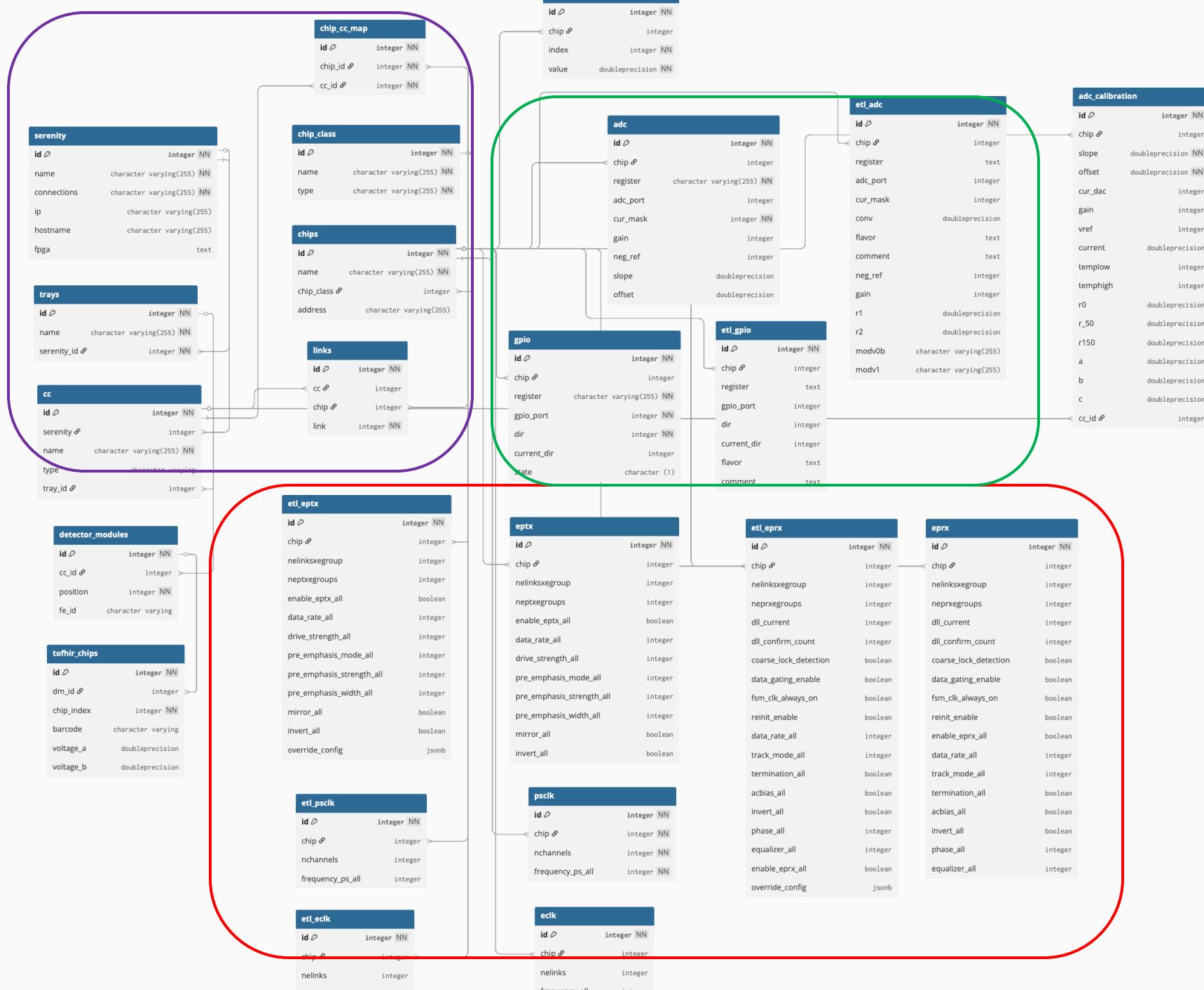

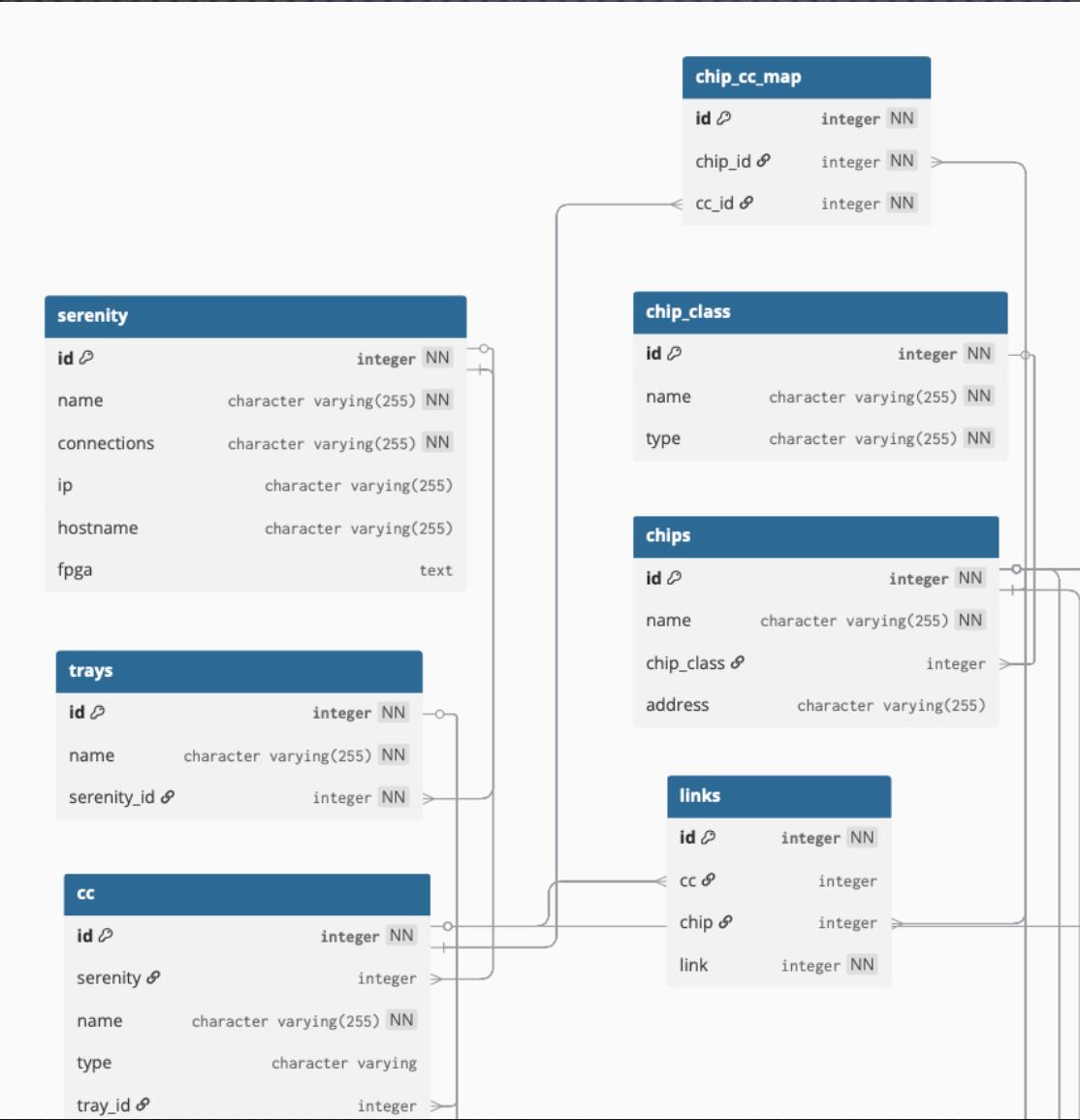

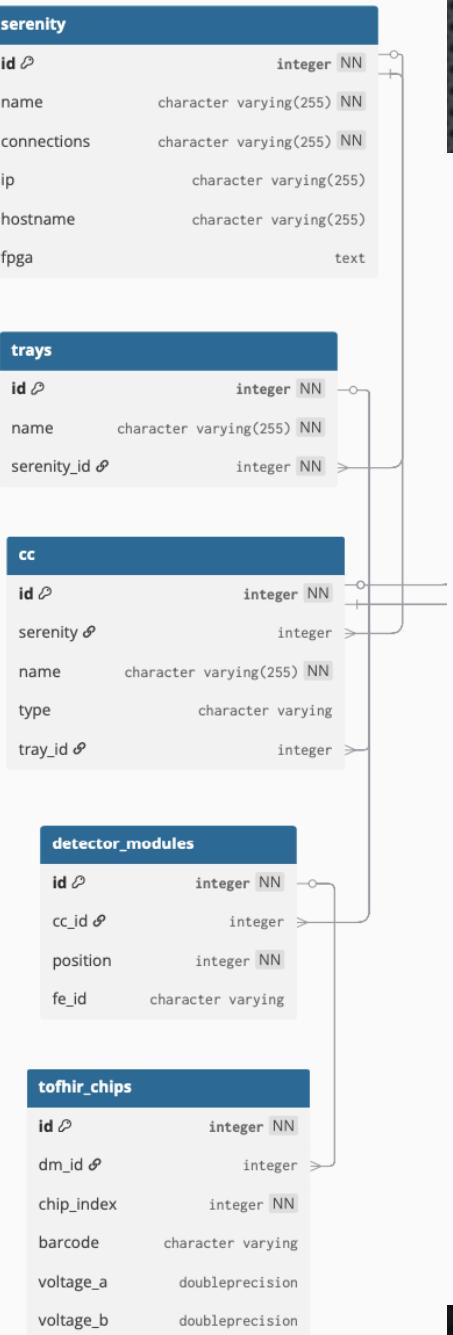

# MTD DAQ DATABASE SCHEMA UPDATE FOR LPGBT CONFIGURATION

## PROBLEM:

- DATABASE SCHEMA DOES NOT FULLY SUPPORT ETL NEEDS

- FOR MUX64 WE DUMP LPGBT REGISTERS TO GET IT WORKING

## PROPOSAL:

- MERGE ETL AND BTL LPGBT CONFIGURATION TABLES INTO ONE TABLE

- STORE ALL LPGBT WRITEABLE REGISTERS IN THE DATABASE

- Goal – `{board_name}/{chip_name}` gives correct configuration

- Instead of just the chip name (ex: LPGBT0, MUX64)

- Agree on uniform table schema between ETL and BTL

- Hold all writeable registers IpGBT registers in DB

- Move towards agnostic language, instead of cc table we have board table

- Goal – {board\_name}/{chip\_name} gives correct configuration

## Proposing Changes:

- Move towards agnostic language

- Keep relations in order to keep BTL SW and Setup working with minimal Disruptions

- Could possibly use Detector\_module table to point to an ETROC\_chips to track connections to RB and Serenity

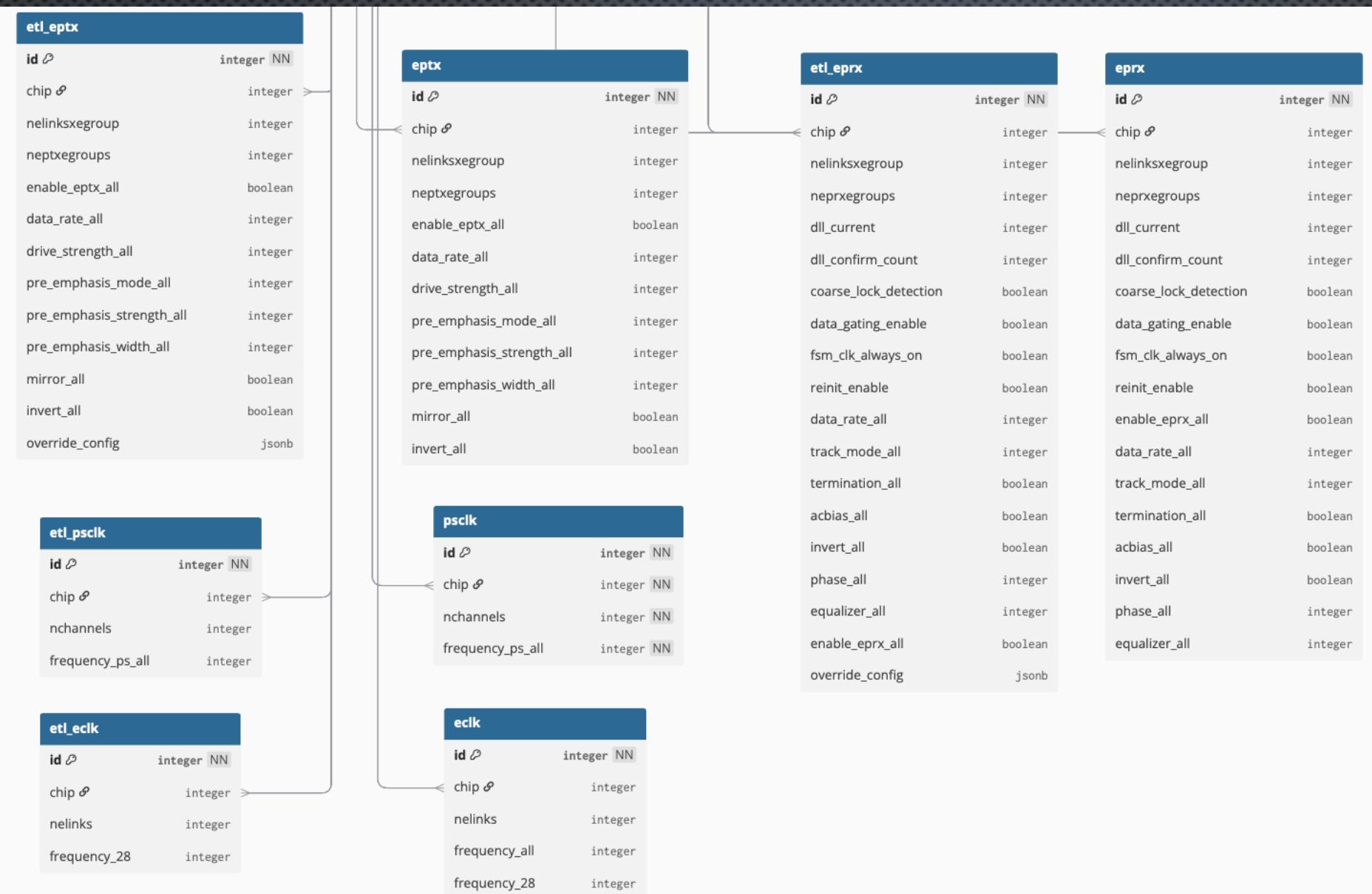

# LPGBT REGS CURRENT SCHEMA

## PROPOSING CHANGES:

- BOTH ETL AND BTL SHOULD USE SAME SCHEMA

- SINGLE TABLE HOLDS ALL WRITEABLE REGISTERS

- FOLLOW LPGBT DOCUMENTATION FOR CHUNKING THE REGISTERS INTO SEPARATE TABLES

- SW FUNCTIONS ALLOW TO READ/WRITE TO GROUP OR SPECIFIC REGISTERS

- E.G DATARATE(1) OR DATARATE(1, CH=3)

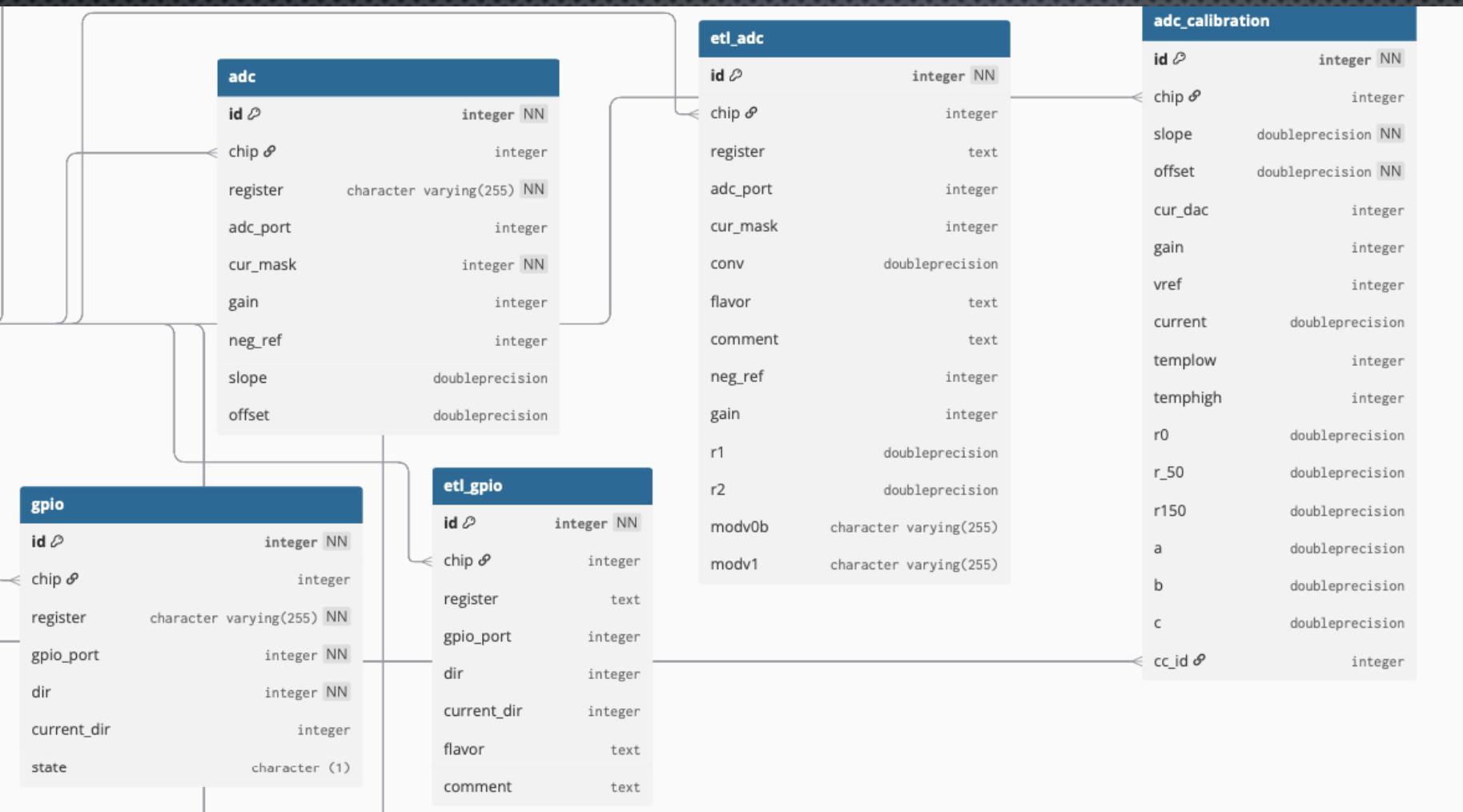

# GPIO/ADC CURRENT SCHEMA

## PROPOSED CHANGES:

- BOTH ETL AND BTL SHOULD USE SAME SCHEMA

- ETL\_ADC TABLE VALUES SHOULD BE MERGED INTO ADC AND ADC CALIBRATION RESPECTIVELY (BASED ON MTD SW NEEDS)

# TOFHIR TABLES REMAIN UNCHANGED

| tofhir.ftp_scan_th_config  | tofhir_disc_scan_config | tofhir_ith1_config      | tofhir_ftp_config  |

|----------------------------|-------------------------|-------------------------|--------------------|

| <b>id</b> <i>Ø</i>         | integer <i>NN</i>       | <b>id</b> <i>Ø</i>      | integer <i>NN</i>  |

| type                       | text <i>NN</i>          | type                    | text <i>NN</i>     |

| threshold                  | text <i>NN</i>          | threshold               | text <i>NN</i>     |

| pre_window                 | text <i>NN</i>          | pre_window              | text <i>NN</i>     |

| post_window                | text <i>NN</i>          | post_window             | text <i>NN</i>     |

| coincidence_window         | text <i>NN</i>          | coincidence_window      | text <i>NN</i>     |

| single_fraction            | text <i>NN</i>          | single_fraction         | text <i>NN</i>     |

| coincidence_time_window    | text <i>NN</i>          | coincidence_time_window | text <i>NN</i>     |

| group_time_window          | text <i>NN</i>          | group_time_window       | text <i>NN</i>     |

| global.c_counter_en        | text <i>NN</i>          | global.c_counter_en     | text <i>NN</i>     |

| global.c_counter_t         | text <i>NN</i>          | global.c_counter_t      | text <i>NN</i>     |

| channel.c_tgr_main         | text <i>NN</i>          | global.c_l1_enable      | text <i>NN</i>     |

| channel.c_count            | text <i>NN</i>          | channel.c_tgr_main      | text <i>NN</i>     |

| channel.c_latch_b          | text <i>NN</i>          | channel.c_count         | text <i>NN</i>     |

| channel.cfg_a2_dcr_delay_e | text <i>NN</i>          | channel.c_latch_b       | text <i>NN</i>     |

| channel.c_min_q            | text <i>NN</i>          | channel.cfg_a3_range_t1 | text <i>NN</i>     |

| channel.c_max_q            | text <i>NN</i>          | channel.cfg_a3_ith_t1   | text <i>NN</i>     |

| global.pulse_amplitude     | text <i>NN</i>          | global.c_aldo_en        | text <i>NN</i>     |

| global.c_ext_tp_en         | text <i>NN</i>          | global.c_aldo_range     | text <i>NN</i>     |

| global.c_ftp_en            | text <i>NN</i>          |                         |                    |

| channel.cfg_a1_ftp_en      | text <i>NN</i>          |                         |                    |

| tofhir_tp_config           |                         | tofhir_tp_config        |                    |

| <b>id</b> <i>Ø</i>         | integer <i>NN</i>       | <b>id</b> <i>Ø</i>      | integer <i>NN</i>  |

| type                       | text <i>NN</i>          | channel.c_tgr_t2        | text <i>NN</i>     |

| threshold                  | text <i>NN</i>          | channel.c_tgr_V         | text <i>NN</i>     |

| pre_window                 | text <i>NN</i>          | channel.c_tgr_B         | text <i>NN</i>     |

| post_window                | text <i>NN</i>          | channel.cfg_a3_ith_t1   | text <i>NN</i>     |

| coincidence_window         | text <i>NN</i>          | channel.cfg_a3_ith_t2   | text <i>NN</i>     |

| single_fraction            | text <i>NN</i>          | channel.cfg_a3_ith_e    | text <i>NN</i>     |

| coincidence_time_window    | text <i>NN</i>          | channel.c_tgr_main      | text <i>NN</i>     |

| group_time_window          | text <i>NN</i>          | global.c_aldo_en        | text <i>NN</i>     |

| channel.c_tgr_main         | text <i>NN</i>          | global.c_aldo_range     | text <i>NN</i>     |

| global.c_tp_en             | text <i>NN</i>          |                         |                    |

| global.c_tp_period         | text <i>NN</i>          |                         |                    |

| global.c_tp_length         | text <i>NN</i>          |                         |                    |

| global.c_tp_inv            | text <i>NN</i>          |                         |                    |

| tofhir_field_metadata      |                         | tofhir_field_metadata   |                    |

| <b>id</b> <i>Ø</i>         | integer <i>NNN</i>      | <b>id</b> <i>Ø</i>      | integer <i>NNN</i> |

| config_type                | text <i>NN</i>          | config_type             | text <i>NN</i>     |

| field_name                 | text <i>NN</i>          | field_name              | text <i>NN</i>     |

| section_name               | text <i>NN</i>          | section_name            | text <i>NN</i>     |

# NEXT STEPS

- I2C DEBUGGING AND WORKING – SERVANT LPGBT AND ETROCs

- ETROC ENCODER + DECODER IN FIRMWARE

- DEPLOY AND TEST NEW DB SCHEMA ON TEST INSTANCE DB

- ADD MTD CONFIGURATOR (API AND DB) CHANGES THAT CONTAINS MERGED ROUTES BETWEEN ETL AND BTL

- MOVE ADC CALIBRATION TO LPGBT CONTROLLER